## 3D Integrated LTCC Module using $\mu$ BGA technology for compact C-band RF Front-End Module

S. Pinel, S.Chakraborty, M.Roellig, R.Kunze, S.Mandal, H.Liang, C-H. Lee, R.Li, K.Lim, G.White, M.Tentzeris and J.Laskar

Packaging Research center, Yamacraw Design Center, School of Electrical and Computer Engineering

Georgia Institute of Technology, Atlanta GA 30332-0269 USA

Fax:(404) 894-5028, Email; pinel@ece.gatech.edu

**Abstract:** This paper presents a novel 3D integration approach for system-on-package (SOP) based solutions for wireless communication applications. This concept has been applied for the 3D integration of a C band Wireless LAN (WLAN) RF front-end module by means of stacking LTCC substrates using  $\mu$ BGA technology. Characterization and modeling of RF vertical board-to-board transition, using  $\mu$ BGA process are presented for the first time. Specific investigations for 5.8 GHz WLAN applications such as high performance embedded band-pass filter design, and a via-fed stacked cavity-backed patch antenna development are reported. GaAs MESFET-based Rx and Tx chipset is implemented in GaAs MESFET process and combined with the suggested package structure, demonstrate 3D integration concept suitable for C-band wireless communication applications.

### I. INTRODUCTION

3D integration approach is a very attractive option to increase density, performance and meet the specifications of the next generation wireless communication systems. Very compact 3D integration technology based on various wafer stacking methods and ultra-thin packaging technology have been successfully proposed for digital applications such as 3D memory and smart cards [1]. However current 3D RF module integration is still based on low density hybrid assembly technologies [2,3]. The development of wireless data communication systems in C-Band leads to very stringent specifications for both IC and packaging performances. For these portable and low-powered applications a high level of integration is also required to reduce essential features as size, weight and interconnection length. Because of the large number of high performance discrete passive components, RF front-end module integration is very challenging. The System-On-Package (SOP) solution (versus the System-On-Chip, SOC), using multi-layer technology has emerged as the most effective approach to achieve simultaneously cost and size reduction, while satisfying the performances and specifications required by these new communication systems. Examples of

implementations on both ceramic and organic substrates have been reported [4-5]. Micro ball grid array ( $\mu$ BGA) technology is currently targeted for low cost RF applications and provides great opportunities for 3D integrated RF front-end module [6].

In this paper, we present a very compact 3D-integration concept suitable for C-band RF front-end module by means of LTCC substrate stacking method using  $\mu$ BGA ball process. Characterization of the RF vertical board-to-board transition and an accurate  $\mu$ BGA ball modeling are reported for the first time for RF applications. A high performance second order narrow-band band-pass filter design, with two cascaded coupled line sections, for C-band, and a via-fed stacked cavity-backed patch antenna designed to fully cover the required band (5.725-5.825 GHz), embedded in multiplayer LTCC substrate are presented. GaAs MESFET-based Rx and Tx chipset development is presented, and combined with the suggested package structure.

### II. 3D INTEGRATED MODULE CONCEPT.

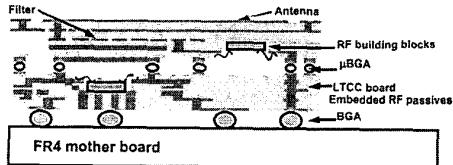

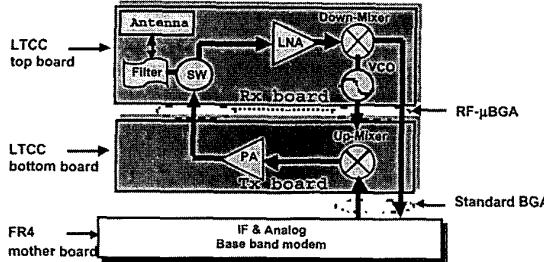

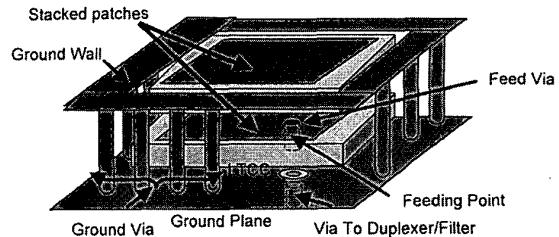

Figure 1 illustrates the proposed module concept. Two stacked LTCC substrates are used and board-to-board vertical transition is insured by  $\mu$ BGA balls. Standard alignment equipment is used to stack the board and thus provide a compact, high performance and low cost assembly process. Multi-stepped cavities into the LTCC boards provide spacing for embedded RF active devices and thus lead to significant volume reduction by minimizing the gap between the boards. Active devices can be flip-chipped as well as wire-bonded. Cavities provides also integration opportunity for MEMS devices such as MEMS Switch. Passive components, off-chip matching networks, embedded filter and antenna are implemented directly into the LTCC boards by using multi-layer technology [4]. Standard BGA balls insure interconnection of this high density module with a mother board such as FR4 board. The top and the bottom substrates are dedicated respectively to the receiver and transmitter building blocks of the RF front-end module. Figure 2 shows the block diagram of each board. The receiver board includes antenna, band-pass filter, active Switch, LNA, VCO and Down-conversion Mixer. The Transmitter board includes Up-conversion Mixer, PA and

off-chip matching networks. Ground planes and vertical via walls [7] are used to address isolation issues between the transmitter and the receiver functional blocks. Arrays of vertical via are added into the transmitter board to achieve better thermal management.

Fig. 1. 3D integrated module concept view.

Fig. 2. Rx and Tx board block diagram.

### III. CHARACTERIZATION AND MODELLING OF THE BOARD TO BOARD TRANSITION.

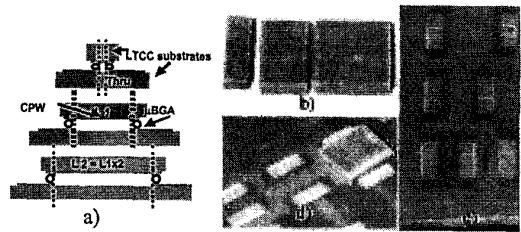

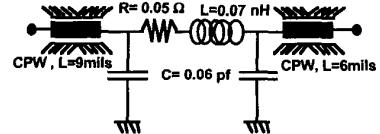

Special care is required in the board-to-board transition to maintain ground, 50-Ohms matching continuity and address coupling and resonance issues. It has been shown that CPW line is the best configuration to avoid vertical coupling between the board and the IC in BGA and flip-chip technology [8]. However the significant reduction of the gap between the two stacked boards, caused by using  $\mu$ BGA ball process, arouses the need of modified CPW design. An accurate model for the  $\mu$ BGA balls is also required to optimize the RF vertical transition design. Figure 3 describes the three structures which have been designed for the characterization of  $\mu$ BGA balls. Thin film metal (Au) is deposited on the top and bottom LTCC boards and then photo-patterned and etched to form the circuitry. 4 mils diameter  $\mu$ BGA solder balls (Sn63Pb37-183°C), standard alignment equipment and conventional reflow process (maximum temperature: 230 °C) have been used to stack the board. Both TRL calibration and TLL de-embedding techniques proposed in [8] have been used to extract S-parameters of the CPW line. Afterwards, these parameters and the overall measurement data have been inserted into a circuit schematic in HP-ADS. Using a fitting-to-measurement method, we have set up a modified model for the CPW and developed a hybrid equivalent circuit model for the  $\mu$ BGA RF transition.

Fig. 3. Board-to-board transition test structures schematic (a) photos of the top (b), bottom (c) and stacked (d) substrates.

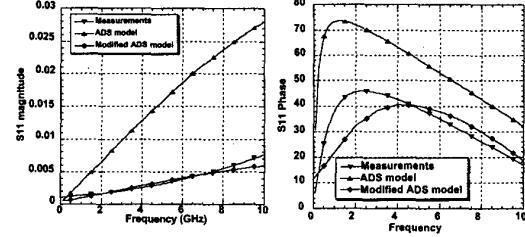

Figure 4 demonstrates the effects of the modification into the model to obtain the accurate CPW behavior. A combination of RLC  $\Pi$ -network and transmission line model is applied to model the  $\mu$ BGA ball. In figure 5a, C represents the effect from the metalization overlap area, R accounts for the parasitic resistance and L the inductance for the self inductance of the balls. The two transmission line sections are added to model accurately the phase responses of S11 and S21. This model predicts insertion loss less than 0.1 dB and return loss about -17dB up to 10 GHz. Figure 5b shows the extracted performances of a single ball transition. Post full wave simulations have also been performed to validate the developed models.

Fig. 4. Modified CPW model.

Fig. 5a. Extracted  $\mu$ BGA hybrid model

Fig. 5b. Extracted  $\mu$ BGA S-parameters.

#### IV. LTCC BOARD DEVELOPMENT

We have first focused our studies on the receiver board. In order to predict the module performances, an accurate modeling and optimization of the whole package is required. All the packaging elements along the RF path have to be considered, namely the RF input and output pads, embedded filter, multiple stacked vertical via, transition between different types of transmission lines, material discontinuity, wire-bonding. The module design is based on a 10 layers LTCC process whose the main features are described in Table 1. Copper metalization and filled vertical via technologies are used to improve electrical performances.

TABLE 1: LTCC process features.

| $\epsilon_r$ | Tan $\delta$ | Dielectric Thickness | Line width And spacing | Via diameter |

|--------------|--------------|----------------------|------------------------|--------------|

| 5.8          | 1.2e-3       | 4 mils               | 4 mils                 | 4 mils       |

We've assigned each layer as following: layer 1 to 5 are dedicated for the embedded filter and layer 6 to 10 are dedicated for vertical interconnections and multi-stepped cavities design. Total size of the receiver board, including the RF chipset, is  $7.8 \times 6 \times 0.9\text{mm}^3$ .

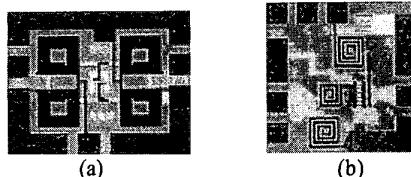

##### A. Embedded Band-pass filter

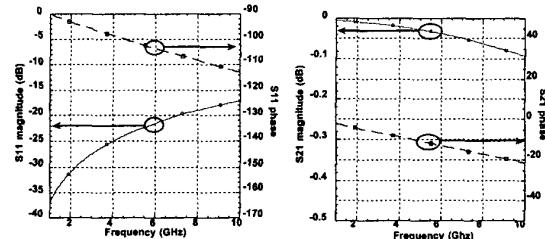

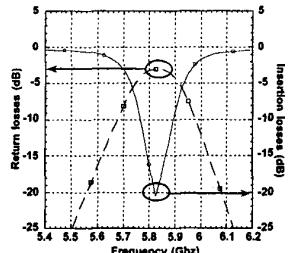

We have developed a high performance second order narrow-band band-pass filter with two cascaded coupled line sections embedded in strip-line configuration to improve insertion loss. A schematic view is presented in figure 6. Coupled lines have been bent to fit into the module shape and via walls are used to connect ground planes and reduce parallel plate modes. Filter performances has been measured separately and exhibit a  $-2.9\text{dB}$  insertion loss,  $-20.8\text{dB}$  return loss, about 200 MHz bandwidth and image rejection greater than  $-20\text{ dB}$  as shown in figure 7.

Fig. 6. Band-pass filter design schematic view.

Fig. 7. Measured Band-pass filter performances.

#### B. Embedded Antenna

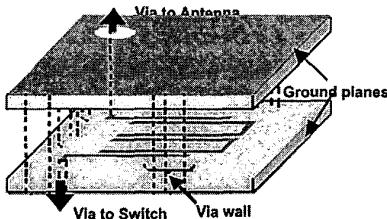

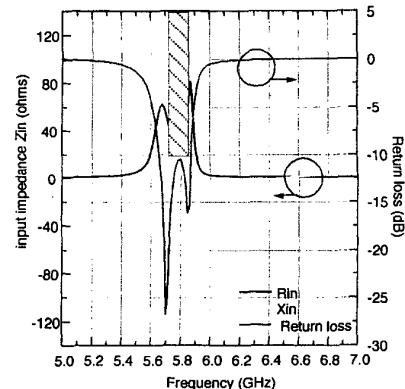

A via-fed stacked cavity-backed patch antenna has been designed for IEEE 802.11a 5.8 GHz band as shown in Fig. 8. The heights of the lower and upper patches (400 mils  $\times$  400 mils) are respectively 8 mils (2 LTCC GL550 layers) and 32 mils.

Fig. 8. Stacked patch antenna for IEEE 802.11a 5.8 GHz band.

The input impedance characteristic of the stacked-patch antenna is shown in Fig. 9. The 10-dB return-loss bandwidth of the antenna is about 4%, fully covering the required band (5.725-5.825 GHz). Also this antenna has a desirable gain (near 6 dBi) and very low cross-polarization (less than  $-35\text{ dBi}$ ).

Fig. 9. Input impedance characteristic of the stacked patch antenna for IEEE 802.11a 5.8 GHz band.

#### V. RX & TX CHIPSET DEVELOPMENT.

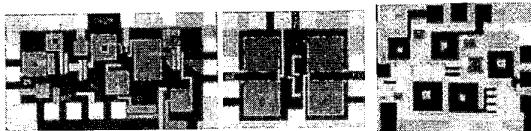

We used commercial 0.6um GaAs MESFET process to implement Rx and Tx chipset. Rx chipset consists in LNA, down converter mixer, and VCO as shown in Figure 10. Tx chipset includes double balanced diode ring mixer and RF amplifier as shown in Figure 11.

Fig. 10. Photo of the Rx chipset used in the module (a) LNA

(b) Mixer (c) VCO

Fig. 11. Photo of the Tx chipset used in the module (a) Mixer

(b) RF amplifier

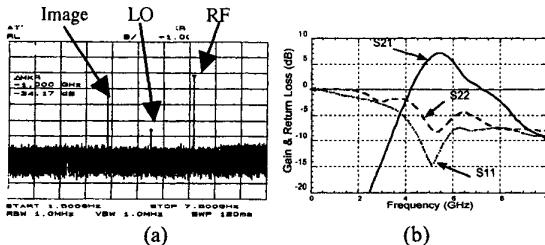

The LNA gain is about 13, the LNA noise is about 2.2 dB. Figure 13 (a) shows the output spectrum of the transmitter mixer demonstrating image signal rejection of 11 dBc, and LO-to-RF rejection of 40 dB, across the VCO tuning range between 4.5 GHz to 5.5 GHz. It also shows less than 11 dB conversion loss between IF frequency from DC to 1 GHz. The RF amplifier demonstrates a measured gain of 7 dB and 1-dB compression point of 17 dBm as shown in Figure 13 (b).

Fig. 13. Tx module performances (a) Mixer output spectrum

(b) RF amplifier gain

## VI. CONCLUSION

We have presented a very compact 3D-integration concept, based on two stacked LTCC substrates connected by means of  $\mu$ BGA balls. Characterization of the board-to-board transition and an accurate  $\mu$ BGA ball modeling are reported for the first time in RF applications. A high performances second order narrow-band band-pass filter with two cascaded coupled line sections has been presented. A via-fed stacked cavity-backed patch antenna has been designed to fully cover the required band (5.725-5.825 GHz) and implemented in multiplayer LTCC substrate. A GaAs MESFET-based (0.6um process) Rx and Tx chipset was implemented, combined with the suggested package structure, demonstrate 3D integration

concept suitable for C-band wireless communication applications. The proposed concept is also applicable to others telecommunications systems towards more miniaturization.

## ACKNOWLEDGEMENT

The authors wish to acknowledge KYOCERA Inc, Triquint Semiconductor, the Packaging Research Center of Georgia-Tech, Zeland software, Florent Cros and Christophe Courcimault at the Microelectronic Research Center of Georgia-Tech, for their technical support.

## REFERENCES

- [1] O.Vendier, M.Huan, C.Drevon, JL. Cazaux, E.Beyne, R.Van Hoof, A.Marty, S.Pinel, J.Tasselli, S.Marco, JR.Morante. "UltrathinElectronics for space applications," *IEEE Electronics components and technology Conference*, p767-771, 2001.

- [2] P.Monfraix, P.Ulian, P.Drevon, C.George, Vera A.C, Tronche, C.Cazaux, J.L.Llopis, O.Graffeuil, "3D microwaves modules for space applications Microwave," *IEEE MTT-S International Symposium Digest*, Vol. 3, Page(s): 1289-1292, Dec. 2000.

- [3] Sturdivant, R. Chung Ly, Benson, J.Hauhe. "Design and performance of a high density 3D microwave module," *IEEE MTT-S International Microwave Symposium Digest*, Vol. 2, page(s):501-504, 1997.

- [4] Kyuate Lim, A.Obatoyinbo, A.Sutuno, S.Chakraborty, C.Lee, E.Gebara, A.Raghavan, J.Laskar. "A highly integrated transceiver module for 5.8Ghz OFDM communication system using Multi-layer packaging technology," *IEEE MTT-S International Microwave Symposium Digest*, Volume: 1, Page(s): 65-68, 2001.

- [5] Diels, W.Vaes, K.Wambacq, P.Donnay, S.De Raedt, W.Engels, M.Bolsens "A Single-package integration of RF blocks for a 5 GHz WLAN application," *Advanced Packaging, IEEE Transactions on Components, Packaging and Technology, Part B: Vol. 24 Issue: 3, Page(s): 384 -391*, Aug. 2001.

- [6] M.F. Caggiano, J.Ou, S.Bulumulla, D.Lischner, "RF Electrical Measurements of Fine Pitch BGA Packages", *IEEE Transaction On Components And Packaging Technologie*, Vol. 24, No. 2, June 2001, 233.

- [7] MJ.Hill, RW.Ziolkowski, J.Papapolymerou, "Simulated and measured results from a Duroid-based planar MBG cavity resonator filter," *J.IEEE Microwave and Guided Wave Letters*, Volume: 10 Issue: 12, Page(s): 528-530, Dec. 2000.

- [8] Hongwei Liang; J.Laskar, M. Hyslop, R.Panicker, "Development of a 36 GHz millimeter-wave BGA package," *IEEE MTT-S International Microwave Symposium Digest*, Volume: 1, Page(s): 65 -68 vol.1, 2000.